# High Performance Computing with CUDA

### **Supercomputing 2009 Tutorial**

David Luebke

**NVIDIA Research**

### Welcome!

#### GPUs have become a major force in HPC

- National & commercial supercomputer installations

- Changing the landscape with "personal supercomputing"

- Emerging ecosystem of tools, vendors, languages, codes

- GPU codenamed "Fermi" will accelerate this trend

- ECC, 8x double precision performance

- Powerful development, debugging, profiling tools

- CUDA programming model

- Tools, languages, and libraries for GPU computing

- Advanced CUDA: optimization, irregular parallelism

#### Case studies:

- CFD

- Seismic processing

- QCD

- Molecular dynamics

#### nobody cares about theoretical peak

#### Challenge:

harness GPU power for real application performance

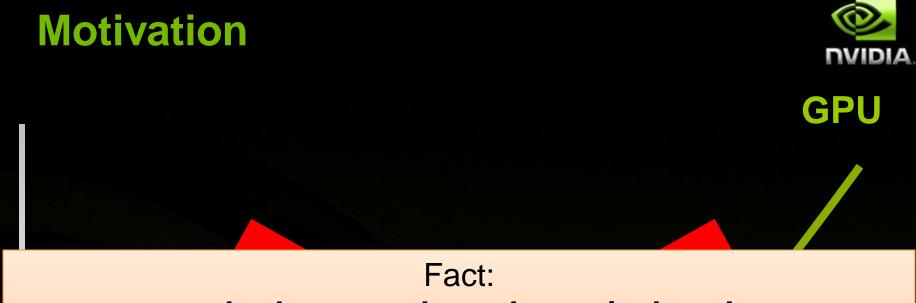

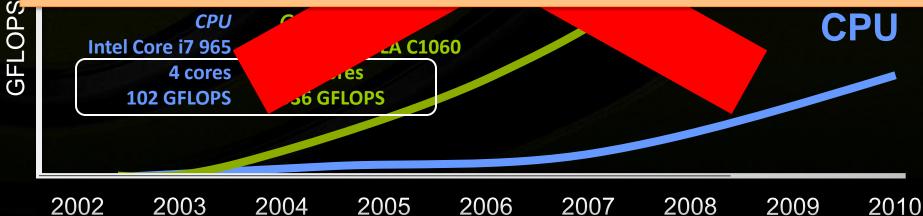

# **Motivation: Accelerating Insight**

© NVIDIA Corporation 2009

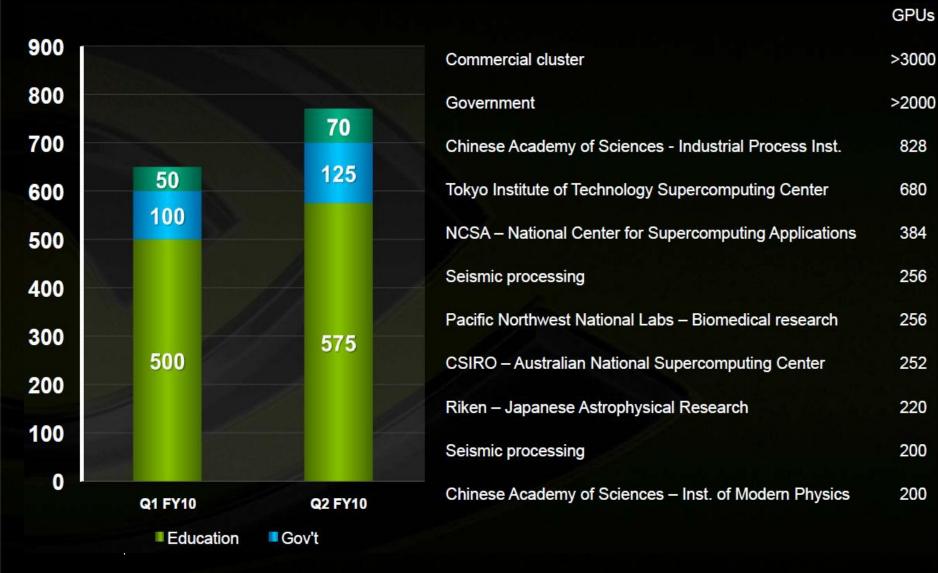

## **CUDA is everywhere**

Over 270 universities teach CUDA Over 2500 research papers

CUDA powered supercomputers

**180 Million CUDA GPUs**

100,000 active developers

639 CUDA applications and counting

**NVIDIA GPUs at Supercomputing 09**

#### 12% of papers use NVIDIA GPUs

#### **GPU-based Paper by Hamada up for Gordon Bell**

# Jack Dongarra, ORNL, Sandia, Los Alamos, Matsuoka speaking at NVIDIA Booth

#### 20+ System Providers are demoing Tesla GPUs

HP, Dell, Cray, Bull, Appro, NEC, SGI, Sun, SuperMicro, Penguin, Colfax, Silicon Mechanics, Scalable, Verari, Tycrid, Mellanox, Creative Consultants, Microway, ACE, TeamHPC

#### 11+ Software Providers building on CUDA GPUs

Microsoft, The Mathworks, Allinea, TotalView, Accelereyes, EM Photonics, Tech-X, CAPS, Platform Computing, NAG, PGI, Wolfram

#### LANL, ORNL, SLAC, TACC, GaTech, HPC Advisory Council, Khronos Group showing GPU Computing Demos

# GPUs in high-performance computing

#### **CUDA** is in products from laptops to supercomputers

# **Emerging HPC Products**

### New class of hybrid GPU-CPU servers

#### SuperMicro 1U GPU Server

Upto 18 Tesla M1060 GPUs

Bull Bullx Blade Enclosure

## **Tutorial goals**

A detailed introduction to high performance computing with CUDA

#### We emphasize:

- Understanding the architecture & programming model

- Core computational building blocks

- Libraries and tools

- Optimization strategy & tactics

#### Case studies to bring it all together

### **Tutorial prerequisites**

- Tutorial intended to be accessible to any savvy computer or computational scientist

- Helpful but not required: familiarity with data-parallel algorithms and programming

Target audience: HPC practitioners using or considering CUDA

### **Speakers:**

### In order of appearance:

- David Luebke NVIDIA

- Ian Buck

NVIDIA

- Jonathan Cohen

- John Owens

- Paulius Micikevicius

- Scott Morton

- John Stone

- Mike Clark

NVIDIA NVIDIA University of California Davis NVIDIA Hess University of Illinois Urbana-Champaign

#### Harvard

#### 8:30 Introduction

Welcome, overview, CUDA basics

### 9:00 CUDA programming environments

Toolchain, languages, wrappers

### Buck

Luebke

#### 10:00 Break

**10:30 CUDA libraries & tools**

MAGMA & CULA, Thrust, CuFFT, CuBLAS... CUDA-gdb, Visual Profiler, codename "Nexus"...

### **11:15 Optimizing GPU performance**

#### Micikevicius

#### 12:00 Lunch

#### **1:30 Optimizing CPU-GPU performance**

#### **Micikevicius**

Owens

#### **1:45 Irregular algorithms & data structures** Sparse linear algebra, tree traversal, hash tables

### **Schedule: case studies**

### 2:30 Molecular modeling

#### 3:00 Break

3:30 Seismic imaging

Morton

4:00 Computational fluid dynamics

Cohen

5:00 Quantum Chromodynamics

Clark

#### 5:00 Wrap!

# **CUDA Basics**

Programming model & simple examples

David Luebke

Thread

#### local memory Local barrier Kernel foo() uuuuuu ttittittitt **Global barrier** per-device global Kernel bar() memory mmmm . . .

### **CUDA In One Slide**

per-thread

per-block

shared

memory

Block

### **CUDA C Example**

```

void saxpy_serial(int n, float a, float *x, float *y)

for (int i = 0; i < n; ++i)

y[i] = a*x[i] + y[i];

Serial C Code

}

// Invoke serial SAXPY kernel

saxpy_serial(n, 2.0, x, y);

_global__ void saxpy_parallel(int n, float a, float *x, float *y)

int i = blockIdx.x*blockDim.x + threadIdx.x;

if (i < n) y[i] = a*x[i] + y[i];

}

Parallel C Code

// Invoke parallel SAXPY kernel with 256 threads/block

int nblocks = (n + 255) / 256;

saxpy_parallel<<<nblocks, 256>>>(n, 2.0, x, y);

```

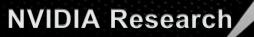

### **Heterogeneous Programming**

### Use the right processor for the right job

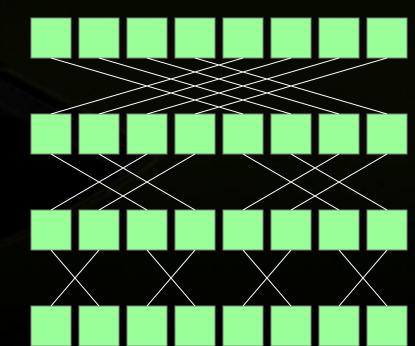

### **Example: Parallel Reduction**

Summing up a sequence with 1 thread:

int sum = 0;

for(int i=0; i<N; ++i) sum += x[i];</pre>

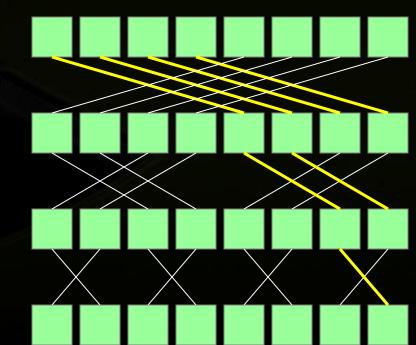

### Parallel reduction builds a summation tree

- each thread holds 1 element

- stepwise partial sums

- N threads need log N steps

- one possible approach: Butterfly pattern

### **Example: Parallel Reduction**

Summing up a sequence with 1 thread:

int sum = 0;

for(int i=0; i<N; ++i) sum += x[i];</pre>

### Parallel reduction builds a summation tree

- each thread holds 1 element

- stepwise partial sums

- N threads need log N steps

- one possible approach: Butterfly pattern

## **Parallel Reduction for 1 Block**

int i = threadIdx.x;

shared int sum[blocksize];

// One thread per element

sum[i] = x\_i; \_\_syncthreads();

for(int bit=blocksize/2; bit>0; bit/=2)

int t=sum[i]+sum[i^bit]; \_\_syncthreads();

sum[i]=t; \_\_syncthreads();

// OUTPUT: Every thread now holds sum in sum[i]

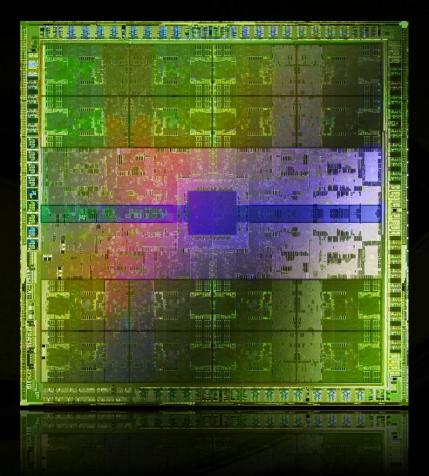

# **Codename "Fermi"**

## Next-Gen GPU: codename Fermi

- 3 billion transistors

- 512 CUDA cores

- ~2x the memory bandwidth

- L1 and L2 caches

- 8x the peak fp64 performance ECC

- C++

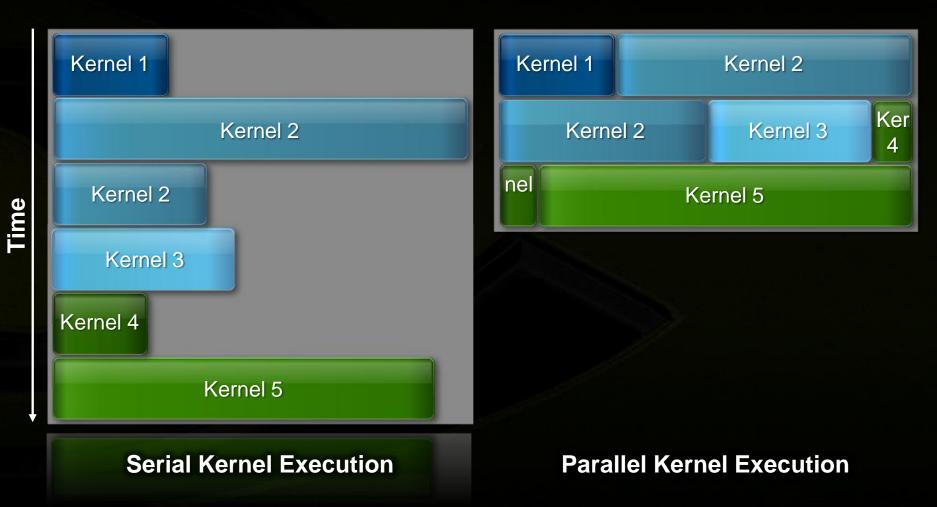

## **Hardware Thread Scheduling**

#### **Concurrent kernel execution + faster context switch**

### **More Fermi Goodness**

- Unified 40-bit address space for local, shared, global

- Configurable 64K L1\$ / shared memory

- 10x faster atomics

- Dual DMA engines for  $CPU \leftarrow \rightarrow GPU$  transfers

- IEEE 754-2008: Fused Multiply-Add (FMA) for SP, DP

### Conclusion

### GPUs are massively parallel manycore computers

- Ubiquitous most successful parallel processor in history

- Useful users achieve huge speedups on real problems

#### CUDA is a powerful parallel programming model

- Heterogeneous mixed serial-parallel programming

- Scalable hierarchical thread execution model

- Accessible many languages, OSs, vendors

They provide tremendous scope for innovation

# **Questions?**

dluebke@nvidia.com

## At the NVIDIA booth (#2365)

- GPU Computing Poster Showcase (Monday 7pm 9pm)

- Demo of Next Generation "Fermi" Architecture

- 3D Internet Demo Cloud Computing with NVIDIA RealityServer

- NVIDIA Theater, including talks by:

Jack Dongarra (Univ of Tenn)

Jeff Vetter (Oak Ridge Nat'l Lab)

Pat McCormick (Los Alamos Nat'l Lab)

Mike Clark (Harvard Univ)

Ross Walker (San Diego Supercomputing Center / UCSD)

**Bill Dally** (NVIDIA)

Satoshi Matsuoka (Tokyo Institute of Tech)

Paul Crozier (Sandia Nat'l Lab)