Um mit der Geschäftsgeschwindigkeit Schritt halten zu können und Beschleunigung in großem Maßstab zu ermöglichen, benötigen Exascale-HPC- und KI-Modelle mit Billionen-Parametern nahtlose Hochgeschwindigkeitskommunikation zwischen allen Grafikprozessoren in einem Servercluster.

Mit der vierten Generation von NVLink kann die Eingabe und Ausgabe (IO) mehrerer Grafikprozessoren mit NVIDIA DGX™- und HGX™-Servern mit 900 Gigabyte pro Sekunde (GB/s) bidirektional pro Grafikprozessor skaliert werden, was mehr als der 7-fachen Bandbreite von PCIe Gen5 entspricht.

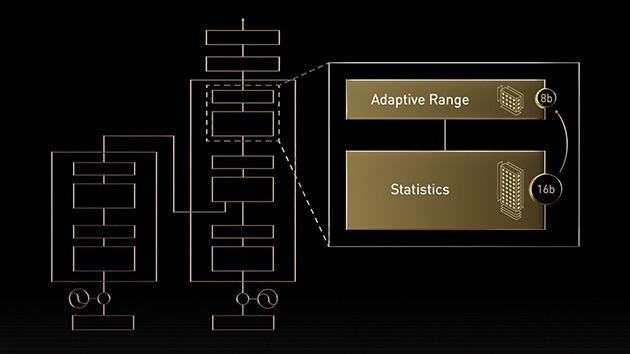

Der NVIDIA NVSwitch™ der dritten Generation unterstützt das netzwerkinterne Scalable Hierarchical Aggregation and Reduction Protocol (SHARP)™ -Computing, das bisher nur auf Infiniband verfügbar war, und bietet eine 2-fache Steigerung des gesamten Durchsatzes innerhalb von acht H200- oder H100-Grafikkarten-Servern im Vergleich zu vorherigen A100-Tensor-Core-Grafikkarten-Systemen.

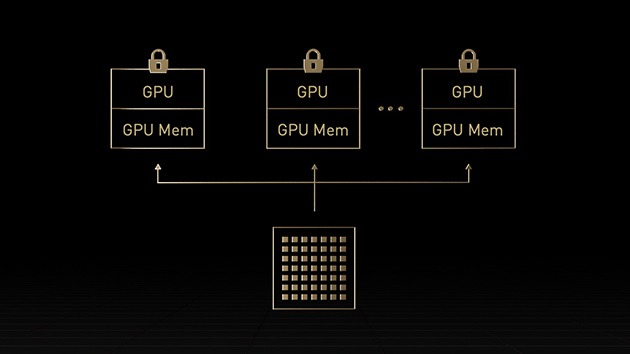

DGX GH200-Systeme mit NVLink-Switch-System unterstützen Cluster mit bis zu 256 verbundenen H200 und bieten eine Gesamtbandbreite von 57,6 Terabyte pro Sekunde (TB/s).